Research Journal of Applied Sciences, Engineering and Technology 8(11): 1326-1330, 2014

DOI:10.19026/rjaset.8.1103

ISSN: 2040-7459; e-ISSN: 2040-7467 © 2014 Maxwell Scientific Publication Corp.

Submitted: May 26, 2014 Accepted: July 01, 2014 Published: September 20, 2014

## **Research Article**

# Design and Development of an Improved Split Row Decoding Algorithm with Reduced BER

<sup>1</sup>B. Rajasekar and <sup>2</sup>E. Logashanmugam

<sup>1</sup>Faculty of Electrical and Electronics,

<sup>1, 2</sup>Sathyabama University, Jeppiaar Nagar, Rajiv Gandhi Salai, Chennai, India

**Abstract:** An optimized split row algorithm is to be developed to reduce effectively the Bit Error Rate effectively. The usage of LDPC codes, especially in the error correction schemes, is tremendously increasing in the modern era. In the conventional approach, the entire matrix which is computed always leads to computational complexity. As for this, the matrix is split into two equal halves and then error checking is done. In such case, it is difficult to judge which partition has to be taken first. Also, it is necessary to reduce the Bit Error Rate. In this Study a novel technique based on fixing appropriate distance between bits and checking it with a predefined condition. It is also observed that as the number of iterations increases, BER decreases.

**Keywords:** BER, error rate, LDPC codes, split row

#### INTRODUCTION

In the past, considerable work was done to enhance the performance of error correction codes where communication over noisy channels was possible near the Shannon limit defined by sparse random graphs using probability-based message-passing algorithms (MacKay, 1999, 2003; MacKay and Neal, 1997). Low-Density Parity-Check (LDPC) codes became popular for their error-correction and near-channel-capacity performances. Though it was initially neglected due to its computational complexity, LDPC is now widely used in recent years (Chen et al., 2004, 2005; Chen and Fossorier, 2002). LDPC has relatively low error rate as well as Better Error Performance with large code lengths. As a result, they have been adopted as the forward error-correction method tool for many recent standards, such as Digital Video Broadcasting via satellites (DVB-S2), the WiMAX standard for microwave communications (802.16e) and high-speed systems. It requires many processing nodes and hence typically suffers from large wire dominated circuits operating at low clock rates which is due to large critical path delays caused by the codes 'inherently irregular" and in the global communication patterns. The delay and price ranges which are more by wires are likely to increase in future technologies (Castello Jr. and Lin, 2004; Daisuke et al., 2014; Liu and Yen, 2008). With these concerns in mind, the design of a future LDPC decoder which will require high performance at low power with the following: (i.e.,) A large number of nodes that have a high degree of Inter

connectivity and a large memory capacity with high memory bandwidths is considered.

Earlier methodologies have fruitfully proved some good functionality using sum product algorithm and Min-Sum algorithm. Estimation of Min function has rivaled to reduce the Bit Error Rate. To surmount this, split row threshold algorithm has been developed where the Bit Error Rate was in the order of 10^-1.

In this study, an efficient decoding technique is proposed that determines the optical distance between bits to verify the condition of the decoder. If the condition is not satisfied, then the above process is repeated with previous rows and columns to decode the bits. Regressive decoding results in reduced BER.

# LITERATURE REVIEW

Forney (2001) proposed a novel algorithm wherein any state realization of a code can be put into normal form at the same time without making any essential change in the corresponding graph or in its decoding complexity. Group or linear codes were generated by group or linear state realizations. On a cycle-free graph, well-defined minimal canonical realization and the sum-product algorithm were available. However, the cut-set bound showed that graphs with cycles possessed a superior performance-complexity trade off. Finally a group code could be decoded using the dual graph, with appropriate Fourier transforms of the inputs and outputs which can simplify decoding of high-rate codes.

Tanner et al. (2004) presented a class of algebraically structured Quasi-Cyclic (QC) Low-

Corresponding Author: B. Rajasekar, Faculty of Electrical and Electronics, Sathyabama University, Jeppiaar Nagar, Rajiv Gandhi Salai, Chennai, India

Density Parity-Check (LDPC) codes with their convolutional counter parts. The OC codes were described by sparse parity-check matrices comprised of blocks of circulant matrices. The sparse parity-check representation allowed for practical graph-based iterative message-passing and) decoding. Based on the algebraic structure, bounds on the girth and minimum distance of the codes within were found and as a result several possible encoding techniques were described. The performance of the QC LDPC block codes was compared with that of the randomly constructed LDPC codes for short to moderate block lengths. It was found that the performance of the LDPC convolutional codes was superior to that of the QC codes. Finally, a continuous decoding procedure for the LDPC convolutional codes was described.

Andrea (2004) proposed algorithms that include Kalman filtering and smoothing, the forward backward algorithm for hidden Markov models, probability propagation in Bayesian networks and decoding algorithms with low-density parity check codes. New algorithms for complex detection and estimation problems can also be derived as instances of the summary-product algorithm.

Mohsenin *et al.* (2009a) proposed an improved thresholding method for the Split-Row decoding algorithm. Simulation and synthesis results showed that the new method only required a minor increase in logical complexity and area, while substantially improving the error performance, which can be up to 0.27 dB for a LDPC code in comparison to the Split-Row decoding algorithm. Also the optimal threshold did not have any dependency on channel statistics and decoding iteration.

Mohsenin *et al.* (2009b) introduced Split-Row Threshold algorithm that significantly improved the error performance when compared to the non-threshold Split-Row algorithm, while requiring only a very small increase in hardware complexity. The Multi-Split-Row Threshold decoding algorithm presented in this study enables further reductions in routing complexity for greater throughput with smaller circuit area implementations.

Tinoosh and Bevan (2010) used a Low-Complexity message-Passing (LDPC) algorithm viz. Split-Row algorithm, to implement Low-Density Parity-Check (LDPC) decoders with reduced routing congestions. The work concluded in it stating that the partition of matrices had been done with the help of split-row algorithm using a partition enabled signal.

Hua *et al.* (2013) described a combinatorial approach to estimate the error rate performance of Low-Density Parity-Check (LDPC) codes decoded by quantized soft-decision iterative decoding algorithms. The method was based on efficient enumeration of input vectors with small distances to a reference vector whose elements are selected to be the most reliable values from the input alphabet. Several techniques,

including modified cycle enumeration and the efficient derivation of problematic inputs for finer quantizers from those of coarser ones were employed, to reduce the complexity of the enumeration. The error rate estimate was derived by testing the input vectors of small distances followed by estimation of the contribution of larger distance vectors.

Miyashita *et al.* (2014) presented time-domain analog and digital mixed-signal processing. Analog computation is more energy- and area-efficient at the cost of its limited accuracy, whereas digital computation is more versatile and it derived greater benefits from technology scaling. Besides, design automation tools for digital circuits were much more sophisticated than those for analog circuits. TD-AMS exploited both advantages on implementing a system on chip including functions for which high computational accuracy was not required, such as error correction, image processing and machine learning.

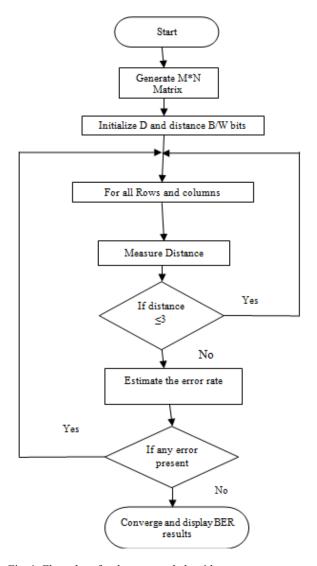

Fig. 1: Flow chart for the proposed algorithm

## **METHODOLOGY**

The proposed algorithm works with the same principle as that of the split-row threshold algorithm. However error correction of bits is different from that of the conventional technique for a defined frame. The actual process lies in fixing the particular distance between bits and checking whether it meets up with the strategy. The strategy involves the data transmission in an AWGN channel where it checks up for only distance of 3 bits. Once it doesn't match with the condition, then it again checks with the earlier row and again the process is on in a sequential manner.

In the proposed method, two types of LDPC decisions namely Hard Decision and Soft Decision techniques are proposed. Finally the BER rate performance is estimated by using the above two methods which is the optimum value when compared with the existing algorithm. The various steps involved in the improved Split-Row Decoding Algorithm are given below:

**Step 1:** Create T and  $D_k$ .

Step 2:  $d = \min\{x: x \in D_k\}, d_m = \infty$ .

**Step 3:** Decode all patterns of distance d to R and corresponding to locations in T.

Step 4: If there are patterns that cannot be correctly decoded,  $d_m = \min \{d, d_m\}$  and update set distance.

Step 5: If  $d_m = \infty$ , d = the next larger distance in  $D_k$ , go to Step 3

**Step 6:** Else generate an error rate estimate.

Step 7: If estimates converge, stop.

Step 8: Else d = the next larger distance in  $D_k$ , go to Step 3.

The proposed technique is shown as flowchart in Fig. 1. Matrix is initially generated and distance between bits and a predefined value D are found. Row and column values are checked pattern-wise and error is measured. If it has any error in the measurement of distance, then it starts from checking the rows and columns once again. If no error is present then further processing begins. It estimates the new error rate if more errors are present. Once again the distance between bits is checked. If it doesn't have any error, then converges to the result, else, the process begins from checking rows and columns.

#### RESULTS AND DISCUSSION

The error performance depends chiefly on the choice of Threshold (T). If the threshold T is larger, local Min1 and Min2 values are smaller than T. It results only when Condition 1 is met and the algorithm converges towards the original Min-Sum Split-Row. On the other hand, if the threshold value is very small, most local minima will be larger than T and only Condition 4 is met which is again the original Min-Sum Split-Row algorithm. The optimum value for T is obtained by empirical simulations. In this study, BPSK modulation and an Additive White Gaussian Noise (AWGN) channel are simulated for all cases. The Proposed technique is compared with the conventional technique

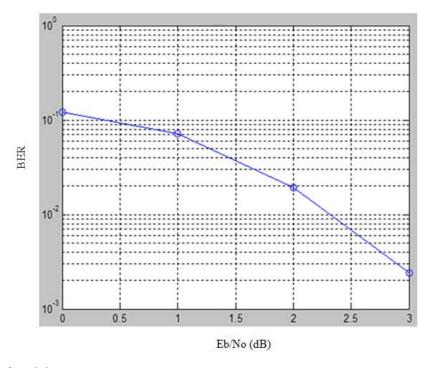

Fig. 2: BER estimate for existing system

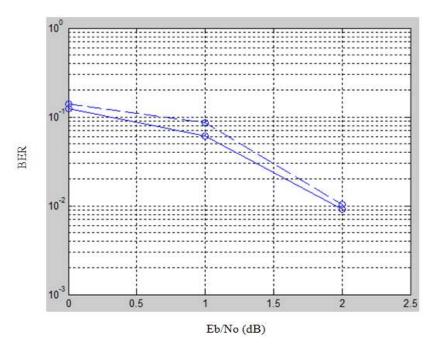

Fig. 3: BER estimate for proposed algorithm (hard decision versus soft decision)

Table 1: Comparison table for different BER vs. SNR with iterations

| SNR | BER                    |                                        |        |        |        |        |

|-----|------------------------|----------------------------------------|--------|--------|--------|--------|

|     |                        | Proposed technique (No. of iterations) |        |        |        |        |

|     | Conventional technique | 5                                      | 10     | 15     | 20     | 30     |

| 1   | 0.0712                 | 0.1195                                 | 0.1289 | 0.1023 | 0.1102 | 0.0605 |

| 2   | 0.0192                 | 0.1125                                 | 0.0512 | 0.0836 | 0.0828 | 0.0092 |

| 3   | 0.0024                 | 0.0504                                 | 0.0609 | 0.0242 | 0.0496 | 0.0007 |

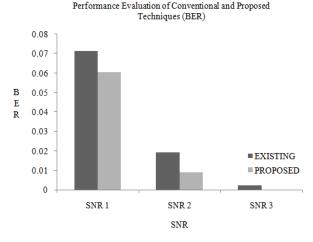

Fig. 4:  $BER_{conventional}$  versus  $BER_{proposed}$  (No. of iterations = 30)

in terms of BER and the outcomes are shown in Fig. 2 and 3. From the figures, it can be concluded that BER of proposed system is optimally better when compared with the other existing systems.

Bit error rate is tabulated for different signal to noise ratios by ranging the number of iterations and are shown in Table 1. From the table it is found that irrespective of SNR, BER decreases as the No. of iteration increases.

In order to assess the performance of the proposed technique, BER of the proposed technique is plotted against BER of the conventional technique as shown in Fig. 4. Number of iterations considered is 30. From the graph, it is found that BER has reduced significantly for the proposed technique when compared to the conventional technique.

# **CONCLUSION**

In this study, the split row threshold algorithm and an improved split row decoding algorithm have been analyzed and an optimizing strategy is also included in the proposed work side. BER has optimally decreased when compared with the existing algorithms. By using the proposed split row decoding algorithm, BER was tabulated for different iterations and simulated as well. It is concluded that BER was 22.8% less than the existing split row-threshold algorithm.

# REFERENCES

Andrea, L., 2004. An introduction to factor graphs. IEEE Signal Proc. Mag., 79(7): 1-31.

- Castello Jr., D.J. and S. Lin, 2004. Error Control Coding. 2nd Edn., Prentice Hall, Upper Saddle River, NJ, USA.

- Chen, J. and M. Fossorier, 2002. Near optimum universal belief propagation based decoding of low-density parity check codes. IEEE T. Commun., 50: 406-414.

- Chen, L., I. Djurdjevic, S. Lin and J. Xu, 2004. Near shannon-limit quasi-cyclic low density parity checks codes. IEEE T. Commun., 52: 1038-1042.

- Chen, J., A. Dholakia, E. Eleftheriou and M. Fossorier, 2005. Reduced complexity decoding of LDPC codes. IEEE T. Commun., 53: 1288-1299.

- Daisuke, M., H. Kazunori and Y. Ryo, 2014. An LDPC decoder with time-domain analog and digital mixed-signal processing. IEEE J. Solid-St. Circ., 49(1): 73-83.

- Forney, G.D. Jr., 2001. Codes on graphs: Normal realizations. IEEE T. Inform. Theory, 47(2): 520-548.

- Hua, X., A.H. Banihashemi and M. Karimi, 2013. Error rate estimation of low-density parity-check codes decoded by quantized soft-decision iterative algorithms. IEEE T. Commun., 61(2): 474-484.

- Liu, C. and S. Yen, 2008. An ldpc decoder chip based on self-routing network for IEEE 802.16e applications. IEEE J. Solid-St. Circ., 43: 684-694.

- MacKay, D.J.C., 1999. Error correcting codes based on very sparse matrices. IEEE T. Inform. Theory, 45: 399-431.

- MacKay, D.J.C., 2003. Information Theory Inference and Learning Algorithms. 3rd Edn., Cambridge University Press, Cambridge, UK.

- MacKay, D.J.C. and R.M. Neal, 1997. Near Shannon limit performance of low density parity check codes. Electron. Lett., 33(6): 457-458.

- Miyashita, D., R. Yamaki, H. Kobayashi, S. Kousai, Y. Oowaki and Y. Unekawa, 2014. An LDPC decoder with time-domain analog and digital mixed-signal processing. IEEE J. Solid-St. Circ., 49: 73-83.

- Mohsenin, T., D. Truong and B. Baas, 2009a. An improved split-row threshold decoding algorithm for LDPC codes. Proceeding of the IEEE International Conference on Communications (ICC '09). Dresden, pp: 1-5.

- Mohsenin, T., D. Truong and B. Baas, 2009b. Multisplit-row threshold decoding implementations for LDPC codes. Proceeding of the IEEE International Symposium on Circuits and Systems (ISCAS, 2009). Taipei, pp. 2449-2452.

- Tanner, R.M., D. Sridhara, A. Sridharan, T.E. Fuja and D.J. Costello, 2004. LDPC block and convolutional codes based on circulant matrices. IEEE T. Inform. Theory, 50(12): 2966-2984.

- Tinoosh, M. and M.B. Bevan, 2010. A split-decoding message passing algorithm for low density parity check decoders. J. Signal Process. Sys., 61(3): 329-345.